Nos sites

eServices

- Annuaire Grenoble-Savoie

- Accès CROMA

- Site de Grenoble

- Site de Chambéry

- Services authentifiés

- Intranet CROMA

- Intranet Grenoble INP

Connexion

Connexion

Connexion

Connexion

> Recherche > CMNE > CMOS & technologies alternatives

> Recherche > CMNE > CMOS & technologies alternatives

L’axe « CMOS » de CROMA jouit d’une réputation internationale reconnue depuis plus de 30 ans en matière de conception et de caractérisation des dispositifs à semi-conducteurs. Il a été notamment pionnier dans l’étude et la promotion des technologies CMOS sur SOI. Notre mission générique consiste à explorer et étendre les frontières de la micro- et nano-électronique CMOS. L’objectif permanent du groupe est la compréhension des mécanismes physiques en vue de leur utilisation pour le développement des technologies, des dispositifs et de leurs applications.

Nos activités de recherche se déroulent notamment dans le contexte du Labex MINOS sur Minatec et en lien étroit avec nos partenaires locaux (CEA, ST, SOITEC, …) et internationaux (réseaux et projets européens, accords bilatéraux…). Elles sont par ailleurs largement soutenues par des projets européens et nationaux.

Nouveaux matériaux et nouvelles architectures MOS

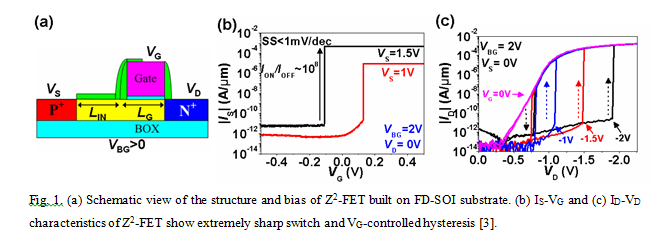

Convaincus que les variantes SOI assureront l’expansion future du CMOS et la transition de la micro- vers la nano-électronique, nous y consacrons beaucoup d’efforts sur deux plans : matériaux et dispositifs. Sur la base des technologies silicium, nous étudions les matériaux alternatifs au silicium massif (SOI, GeOI, Si contraint, SiC, III-V, GaN, etc.) ainsi que les nouvelles architectures de transistors MOS et de mémoires associées. L’accent est mis notamment sur les composants à faible pente sous le seuil pour les applications combinant performance et faible consommation.

Keywords: SOI, ultra-thin body and BOX (UTBB), GeOI, grilles multiples, nanofils(NW), MOSFET III-V, Tunnel FET, steep slope, floating body effects, ReRAM, NVM, variabilité spatiale et dynamique…

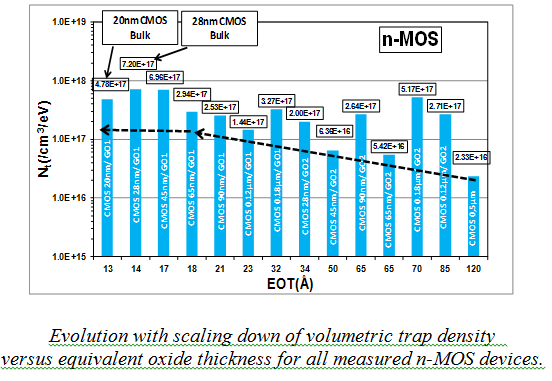

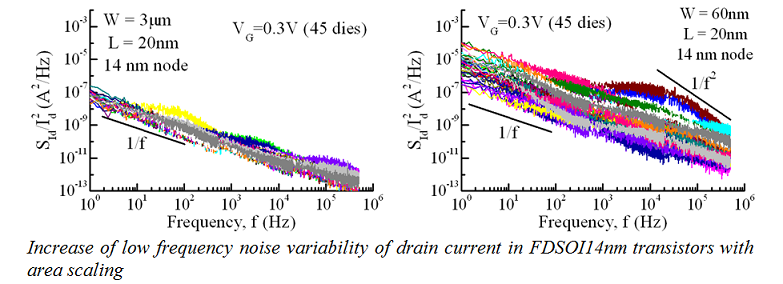

Caractérisation du transport et des interfaces diélectriques

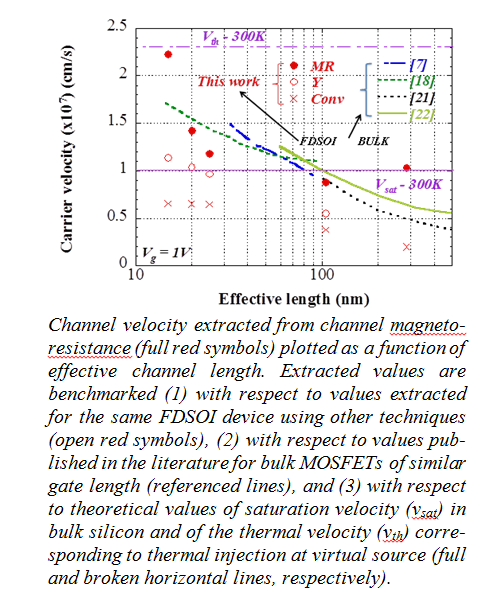

Notre expertise dans ce domaine est fortement sollicitée pour évaluer le potentiel des matériaux alternatifs (pour le canal, la grille et les isolants enterrés), les effets de l'ingénierie de contrainte mécanique dans le canal et l’influence de l’architecture du transistor (films ultra-minces, grilles multiples, FinFET, JLT, nanofils, etc.). Notons que la pertinence d’une option technologique doit toujours être évaluée pour des canaux courts typiques du nœud technologique car les conclusions peuvent différer notablement de celles obtenues en canal long !

Keywords: mobilité des électrons et des trous, vitesse des électrons et des trous, vitesse de saturation, vitesse d’injection thermoïonique, transport hors d’équilibre, processus d’interaction, transport balistique, confinement et couplages quantiques, couplage entre canaux de conduction, inversion volumique, pièges d’interface, défauts…

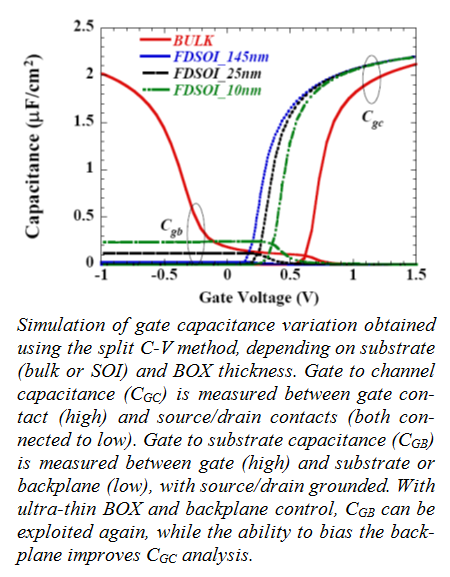

Techniques de caractérisation et des méthodologies d’extraction de paramètres

La compréhension de la physique de ces nouveaux composants passe par la capacité des expérimentateurs à extraire à partir des caractéristiques électriques des paramètres physiquement pertinents caractéristiques des différents phénomènes impliqués (couplage électrostatique, transport électronique, piégeage/dépiégeage des porteurs, effets quantiques, etc). Pour maintenir cette expertise au meilleur niveau mondial, nous développons en permanence nos techniques de caractérisation, les modèles physiques sous-jacents et nos outils de simulation.

Keywords: pseudo-MOS, Y-function, split CV, analyse G-w, transitoires, effet Hall, magnétoresistance de canal, pompage de charge, bruit basse fréquence (LFN), mesures à basse température…

Filières alternatives au silicium

Les filières alternatives au silicium (SiC, GaN, substrats organiques, graphène) constituent également des sujets importants qui, de plus, démontrent notre volonté d’ouverture tout en utilisant à bon escient notre expertise en physique des dispositifs à semi-conducteurs.

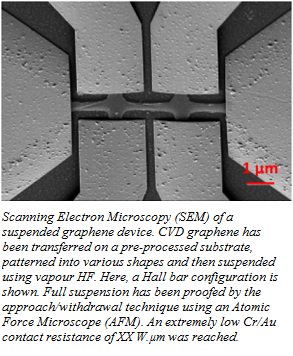

While it has been extensively proven that graphene was featuring many extraordinary properties that make it potentially interesting in a wide variety of fields, its full development will only be possible once scalable and robust fabrication routes compatible with large substrates will be available. This is a real challenge. Graphene growth by CVD on metal catalyst layer and its transfer to any type of substrate are first steps in this direction. However, processing such an ultra-thin layer of organic composition is not straightforward, with many issues to be solved, related for instance to capillary effects, control of ad-hesion, residual strain or incompatibility with some usual cleaning processes. We have succeeded in developing such a route for the fabrication of suspended structures. This opens the field to a variety of applica-tions, for instance in the field of NEMS.

While it has been extensively proven that graphene was featuring many extraordinary properties that make it potentially interesting in a wide variety of fields, its full development will only be possible once scalable and robust fabrication routes compatible with large substrates will be available. This is a real challenge. Graphene growth by CVD on metal catalyst layer and its transfer to any type of substrate are first steps in this direction. However, processing such an ultra-thin layer of organic composition is not straightforward, with many issues to be solved, related for instance to capillary effects, control of ad-hesion, residual strain or incompatibility with some usual cleaning processes. We have succeeded in developing such a route for the fabrication of suspended structures. This opens the field to a variety of applica-tions, for instance in the field of NEMS.

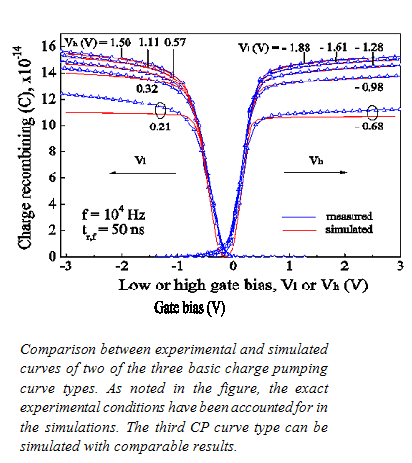

TheCharge pumping (CP) is a technique that applies on MOS transistors and allows the study of semiconductor-insulator interfaces traps. Depending on both, the specific CP technique used and the semiconductor-insulator studied, the mean interface trap density, the trap density vs. energy profile in the semiconductor bandgap, the traps capture cross-section or the trap density vs. insulator depth profile can be extracted. However, until recently, basic CP mecha-nisms were not correctly understood so that the three basic CP curve types had not been simulated satisfactorily. The figure shows two of these three basic curve types and their simulation. From the model that permitted these results, basic CP processes are validated along with the main Si-SiO2 interface traps properties introduced so that deeper studies of Si-SiO2 interface traps become possible.

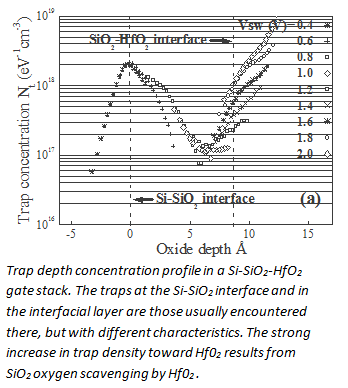

TheCharge pumping (CP) is a technique that applies on MOS transistors and allows the study of semiconductor-insulator interfaces traps. Depending on both, the specific CP technique used and the semiconductor-insulator studied, the mean interface trap density, the trap density vs. energy profile in the semiconductor bandgap, the traps capture cross-section or the trap density vs. insulator depth profile can be extracted. However, until recently, basic CP mecha-nisms were not correctly understood so that the three basic CP curve types had not been simulated satisfactorily. The figure shows two of these three basic curve types and their simulation. From the model that permitted these results, basic CP processes are validated along with the main Si-SiO2 interface traps properties introduced so that deeper studies of Si-SiO2 interface traps become possible.  A few years ago, HfO2, a “high–k” dielectric, has been introduced in production to replace conventional SiO2 as gate insulator (Intel 2007). This allowed to obtain identical channel control with higher dielectric thickness and therefore to reduce gate leakage current (SiO2 thickness < 2 nm at that time). However, in addition to a thin SiO2 interfacial layer that grows during HfO2 deposition, this change impacted carrier mobility, noise level and threshold voltage stability so that a huge effort has been carried out to better characterize these stacks and their interfaces. Charge pumping can be used for that.

A few years ago, HfO2, a “high–k” dielectric, has been introduced in production to replace conventional SiO2 as gate insulator (Intel 2007). This allowed to obtain identical channel control with higher dielectric thickness and therefore to reduce gate leakage current (SiO2 thickness < 2 nm at that time). However, in addition to a thin SiO2 interfacial layer that grows during HfO2 deposition, this change impacted carrier mobility, noise level and threshold voltage stability so that a huge effort has been carried out to better characterize these stacks and their interfaces. Charge pumping can be used for that.

mise à jour le 10 janvier 2024