Soutenance de thèse de Lukas CZORNOMAZ

Publié le 5 janvier 2016

A+Augmenter la taille du texteA-Réduire la taille du texteImprimer le documentEnvoyer cette page par mail

Soutenance de Lukas CZORNOMAZ pour une thèse de DOCTORAT de l'Université de Grenoble, spécialité NANO ELECTRONIQUE ET NANO TECHNOLOGIES, intitulée :

Amphiteatre P014 - Grenoble INP Minatec

3, Parvis Louis Néel CS 50257

38016 Grenoble Cedex 1

« Filière technologique hybride InGaAs/SiGe pour applications CMOS »

Vendredi 22 Janvier 2016 à 10h

Résumé de thèse :

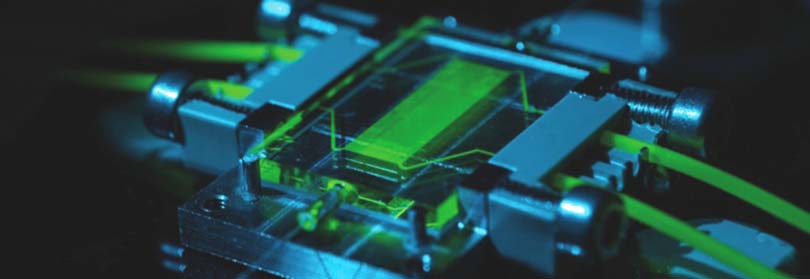

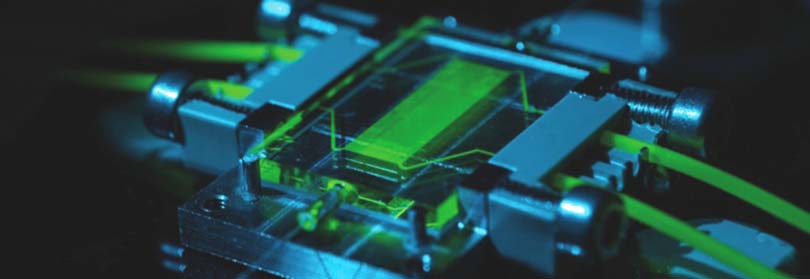

Les materiaux à forte mobilité comme l’InGaAs et le SiGe sont considérés comme des candidats potentiels pour remplacer le Si dans les circuits CMOS futurs. De nombreux défis doivent être surmontés pour transformer ce concept en réalité industrielle. Cette thèse couvre les principaux défis que sont l’intégration de l’InGaAs sur Si, la formation

d’oxydes de grille de qualité, la réalisation de régions source/drain autoalignés

de faible résistance, l’architecture des transistors ou encore la cointégration de ces matériaux dans un procédé de fabrication CMOS. Les solutions envisagées sont proposées en gardant comme ligne directrice l’applicabilité des méthodes pour une production de grande envergure. Substrats L’intégration d’InGaAs sur Si est envisagée sous forme de couches pleines plaques réalisées par collage ainsi que sous forme d’îlots micrométriques cru de manière sélective dans des cavités d’oxyde.

Grâce à la technique du collage pleine plaque, des substrats d’InGaAs sur isolants sur 200 mm ont pu être réalisés avec une densité de défauts inférieure à 3×108 cm2.

Le recyclage de la plaque donneuse est démontré par séparation thermique des plaques induite par une implantation préalable d’hydrogène. Des substrats hybrides bicanaux

d’InGaAs et SiGe sont également fabriqués pour permettre la réalisation de circuits CMOS hybrides. Ensuite, la surcroissance épitaxiale latérale confinée d’InGaAs et d’InP dans des cavités d’oxyde est proposée comme une nouvelle solution pour l’intégration locale de matériaux IIIV sur Si. Modules Des empilements de grille à forte stabilité thermique, contenant une couche intermédiaire de silicium amorphe entre le diélectrique de grille et le canal d’InGaAs, obtiennent une épaisseur de capacité équivalente inférieure à 14 Å. Le phénomène de récupération d’oxygène à distance appliqué aux oxydes natifs d’InGaAs permet d’obtenir une réduction jusqu’à 5 Å de l’épaisseur de capacité équivalente associée à une réduction de la densité de défauts d’interface. Basé sur ces résultats, un empilement de grille optimisé à base de

déposition atomique assistée par plasma est présentée. Des régions source/drain autoalignées sont proposées se basant sur la croissance sélective optimisée de régions semiconductrices fortement dopées. Ces régions recrues sont combinées avec un alliage de NiInGaAs autoaligné, et comparé avec des contacts métalliques directs. Composants Des transistors d’InGaAs autoalignés et compatibles CMOS avec différentes architectures sont comparés : composants sur substrat massif vs sur isolant, planaire vs triple grille, grille en premier vs grille de remplacement, empilement de grille avec ou sans silicium amorphe, alliage NiInGaAs ou contacts métalliques directs. Des

composants triple grille InGaAs sur Si optimisés avec une grille de remplacement, un empilement de grille déposé par couche atomique assistée par plasma et contacts métalliques directs présentent des performances records. Avec une longueur de grille de 50 nm et une largeur de fin de 15 nm, une pente sous le seuil de 80 mV/dec est obtenue avec un courant ON de 156 µA/µm à courant OFF fixé à 100 nA/µm et tension d’opération fixée à 0.5 V. Circuits Des circuits 2D coplanaire hybrides à base d’InGaAs et SiGe sont fabriqués, utilisant le collage pleine plaque ou le procédé de surcroissance épitaxiale latérale confinée. Des inverseurs CMOS ainsi que des cellules mémoire de type 6TSRAM sont obtenues avec succès, ce qui représente la première démonstration de circuits CMOS coplanaires hybrides InGaAs/SiGe sur Si. L’intégration monolithique 3D est proposée pour intégrer une couche ”chaude” inférieure de transistors P en SiGe avec une couche ”froide” supérieure de transistors N en InGaAs ; chaque couche faisant appel au procédé de fabrication optimisé respectif à chaque type de composant.

Des performances excellentes sont obtenues pour chaque type de composants. De même, des inverseurs CMOS 3D sont démontrés.

Membres du jury :

- Sorin CRISTOLOVEANU: Directeur de thèse

- Jean FOMPEYRINE : Coencadrant de thèse

- Alexander ZASLAVSKY : Rapporteur

- Francis BALESTRA: Examinateur

- Luca SELMI : Rapporteur

Siegfried MANTL: Examinateur

A+Augmenter la taille du texteA-Réduire la taille du texteImprimer le documentEnvoyer cette page par mail

Partenaires

Thèse préparée dans le laboratoire : UMR 5130 IMEP-LaHC (Institut de

Microélectronique, Electromagnétisme, Photonique – Laboratoire Hyperfréquences et Caractérisation ), sous la direction de Sorin CRISTOLOVEANU , directeur de thèse .

mise à jour le 5 janvier 2016

Nos sites

eServices

Connexion

Connexion Connexion

Connexion

> Actualites > Soutenance de Thèses

> Actualites > Soutenance de Thèses