Our sites

eServices

- Grenoble-Savoie Directory

- Maps & Directions

- CROMA Grenoble

- CROMA Chambéry

Connexion

Connexion

Connexion

Connexion

> Research > CMNE > Ultimate CMOS

> Research > CMNE > Ultimate CMOS

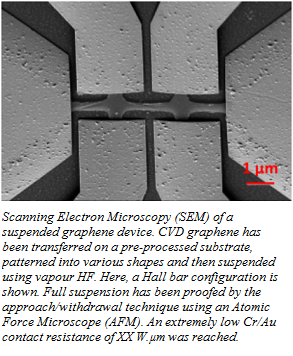

While it has been extensively proven that graphene was featuring many extraordinary properties that make it potentially interesting in a wide variety of fields, its full development will only be possible once scalable and robust fabrication routes compatible with large substrates will be available. This is a real challenge. Graphene growth by CVD on metal catalyst layer and its transfer to any type of substrate are first steps in this direction. However, processing such an ultra-thin layer of organic composition is not straightforward, with many issues to be solved, related for instance to capillary effects, control of ad-hesion, residual strain or incompatibility with some usual cleaning processes. We have succeeded in developing such a route for the fabrication of suspended structures. This opens the field to a variety of applica-tions, for instance in the field of NEMS.

While it has been extensively proven that graphene was featuring many extraordinary properties that make it potentially interesting in a wide variety of fields, its full development will only be possible once scalable and robust fabrication routes compatible with large substrates will be available. This is a real challenge. Graphene growth by CVD on metal catalyst layer and its transfer to any type of substrate are first steps in this direction. However, processing such an ultra-thin layer of organic composition is not straightforward, with many issues to be solved, related for instance to capillary effects, control of ad-hesion, residual strain or incompatibility with some usual cleaning processes. We have succeeded in developing such a route for the fabrication of suspended structures. This opens the field to a variety of applica-tions, for instance in the field of NEMS.

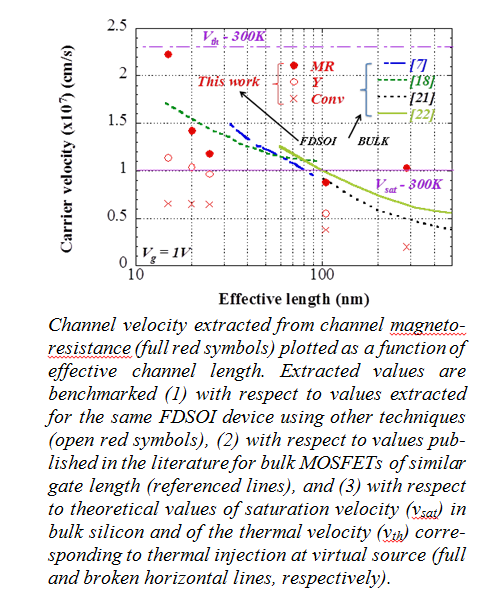

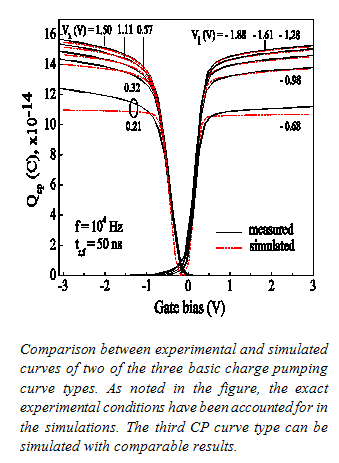

TheCharge pumping (CP) is a technique that applies on MOS transistors and allows the study of semiconductor-insulator interfaces traps. Depending on both, the specific CP technique used and the semiconductor-insulator studied, the mean interface trap density, the trap density vs. energy profile in the semiconductor bandgap, the traps capture cross-section or the trap density vs. insulator depth profile can be extracted. However, until recently, basic CP mecha-nisms were not correctly understood so that the three basic CP curve types had not been simulated satisfactorily. The figure shows two of these three basic curve types and their simulation. From the model that permitted these results, basic CP processes are validated along with the main Si-SiO2 interface traps properties introduced so that deeper studies of Si-SiO2 interface traps become possible.

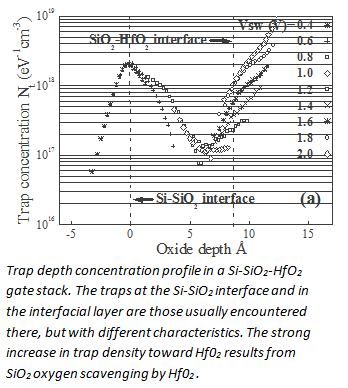

TheCharge pumping (CP) is a technique that applies on MOS transistors and allows the study of semiconductor-insulator interfaces traps. Depending on both, the specific CP technique used and the semiconductor-insulator studied, the mean interface trap density, the trap density vs. energy profile in the semiconductor bandgap, the traps capture cross-section or the trap density vs. insulator depth profile can be extracted. However, until recently, basic CP mecha-nisms were not correctly understood so that the three basic CP curve types had not been simulated satisfactorily. The figure shows two of these three basic curve types and their simulation. From the model that permitted these results, basic CP processes are validated along with the main Si-SiO2 interface traps properties introduced so that deeper studies of Si-SiO2 interface traps become possible.  A few years ago, HfO2, a “high–k” dielectric, has been introduced in production to replace conventional SiO2 as gate insulator (Intel 2007). This allowed to obtain identical channel control with higher dielectric thickness and therefore to reduce gate leakage current (SiO2 thickness < 2 nm at that time). However, in addition to a thin SiO2 interfacial layer that grows during HfO2 deposition, this change impacted carrier mobility, noise level and threshold voltage stability so that a huge effort has been carried out to better characterize these stacks and their interfaces. Charge pumping can be used for that.

A few years ago, HfO2, a “high–k” dielectric, has been introduced in production to replace conventional SiO2 as gate insulator (Intel 2007). This allowed to obtain identical channel control with higher dielectric thickness and therefore to reduce gate leakage current (SiO2 thickness < 2 nm at that time). However, in addition to a thin SiO2 interfacial layer that grows during HfO2 deposition, this change impacted carrier mobility, noise level and threshold voltage stability so that a huge effort has been carried out to better characterize these stacks and their interfaces. Charge pumping can be used for that.Date of update November 17, 2023