Nos sites

eServices

- Annuaire Grenoble-Savoie

- Accès CROMA

- Site de Grenoble

- Site de Chambéry

- Services authentifiés

- Intranet CROMA

- Intranet Grenoble INP

Connexion

Connexion

Connexion

Connexion

> Actualites > Soutenance de Thèses

> Actualites > Soutenance de Thèses

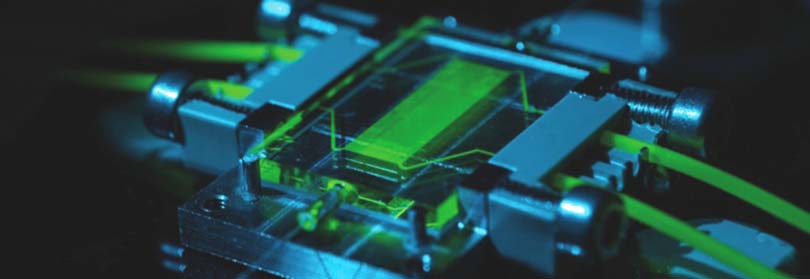

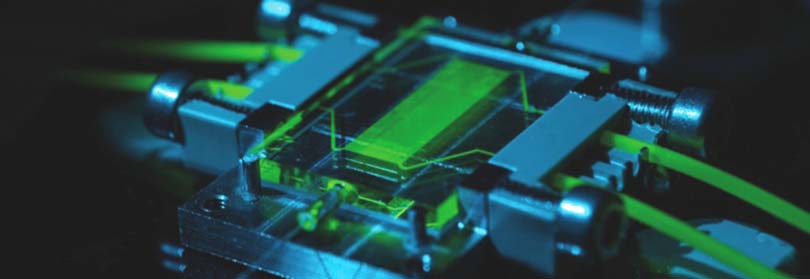

«Caractérisation et modélisation de nouvelles capacités « Through Silicon Capacitors » à forte intégration pour la réduction de consommation et la montée en fréquence dans les architectures 3D de circuits intégrés»

mise à jour le 16 novembre 2016