Résumé :

Au lieu de réduire la taille des transistors pour respecter la loi de Moore, les technologies d'intégration tridimensionnelle (3-D) offrent une densité d'intégration plus élevée, une consommation d'énergie plus faible et fournissent une plateforme unique pour l'intégration hétérogène de différents matériaux de couches actives par l'empilement vertical des couches de circuits intégrés. L'intégration séquentielle 3-D (également appelée intégration monolithique 3-D ou VLSI 3-D) est un type de schéma d'intégration 3-D, dans lequel les multiples couches empilées sont fabriquées séquentiellement l'un sur l'autre sur la même plaquette. Chaque niveau est constitué de couches actives et de couches BEOL isolées par des couches diélectriques intercouches (ILD). La propriété fondamentale qui différencie cette technologie est la reduction importante de la distance entre les 2 (ou plus) couches, qui conduit à des très petites capacités parasites permettant aux signaux numériques d'avoir une haute fréquence tout en étant générés avec une faible énergie.

En conséquence, l'intégration séquentielle 3-D apporte des nouvelles possibilités pour les architectures mixtes avec des performances en termes de vitesse et de faible consommation

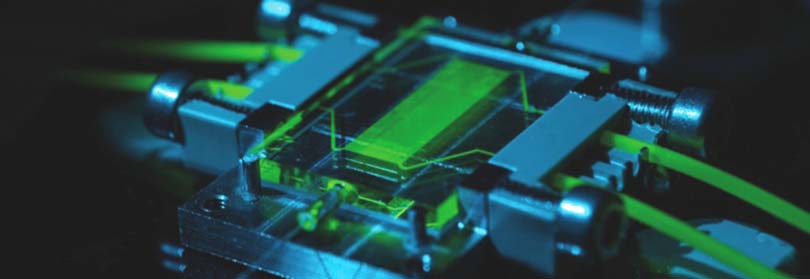

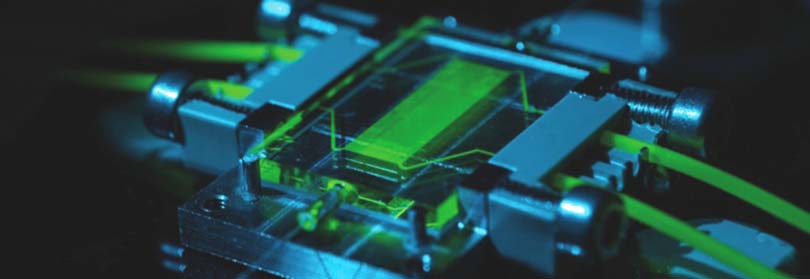

d'énergie qui ne peuvent pas être facilement satisfaites avec d'autres schémas de technologies 3-D (TSV, copper to copper bonding, etc.). Cependant, les signaux à haute fréquence, la localisation spatiale, la forte densité d'interconnexions peuvent tous être une source majeure d'interférence entre les niveaux empilés, modulant le comportement attendu des dispositifs ainsi qu'ajoutant du bruit. Il faut donc trouver des solutions et des techniques pour limiter ces effets. Ce travail vise à répondre à ce défi et assurer la robustesse de la technologie. L'impact de l'interférence électromagnétique et du bruit entre les niveaux empilés dans la technologie d'intégration séquentielle 3-D est étudié de manière approfondie dans ce travail, tant au niveau des dispositifs que des circuits. Pour ce faire, les designs digital, analogiques et signaux mixtes/RF les plus critiques ont été sélectionnées pour construire des circuits 3-D monolithiques. Des mésures électriques, en conjonction avec des simulations TCAD, révèlent les mécanismes de couplage responsables pour la propagation électromagnétique et du bruit entre les niveaux empilés. De plus, la force des signaux propagés est évaluée et son impact sur les performances du dispositif / circuit est étudié en profondeur.

Cette étude présente également l'impact des effets de couplage sur la performance d'un capteur d'image CMOS (CIS) en intégration séquentielle 3-D partitionné en différents niveaux,

est examiné. Le CIS constitue un cas d'étude idéal des effets de couplage car il est constitué de parties très sensibles au bruit, tout en présentant une utilisation extrêmement attrayante de l'intégration séquentielle 3D pour l'industrie de semi-conducteurs. Les chiffres de mérite les plus critiques sont donc analysés au niveau du pixel pour assurer le fonctionnement normal du circuit.

Enfin, une approche de modélisation des effets de couplage entre les niveaux est présentée. Les modèles prédisent avec précision l'impact des effets de disposition sur le couplage capacitif interniveaux entre les dispositifs actifs, et peut être intégré dans les outils SPICE pour analyser des circuits 3-D monolithiques complexes et à grande échelle, en fusionnant le fossé entre les simulations de pré et post-disposition.

Membres du jury

- Dr. Gilles SICARD, Ingénieur de recherche HDR, CEA-Leti, Grenoble : Directeur de thèse

- Dr. Perrine BATUDE, Ingénieure de recherche, CEA -Leti, Grenoble : Co-encadrante

- Dr. Christoforos THEODOROU , Chargé de recherche, IMEP-LAHC, Grenoble : Co-encadrant

- Pr. Per-Erik HELLSTROM, Professeur des Universités, KTH, Stockholm, Suède : Rapporteur

- Pr Cristell MANEUX, Professeure des Universités, IMS, Bordeaux : Rapporteur

- Dr Gérard GHIBAUDO, Directeur de Recherche, IMEP-LAHC, Grenoble : Examinateur

- Pr Pierre MAGNAN, Professeur des Universités, ISAE, Toulouse : Examinateur

Nos sites

eServices

Connexion

Connexion Connexion

Connexion

> Actualites > Soutenance de Thèses

> Actualites > Soutenance de Thèses