INTERNATIONAL ROADMAP FOR DEVICES AND SYSTEMS

### European and International Nanolectronic Roadmaps: from Materials to Systems

#### IMEP-LAHC, April 29, 2020

Francis Balestra, Imep-Lahc

**ICT-CSA: Micro- and Nano-Electronics Technologies** Grant Agreement n° 685559

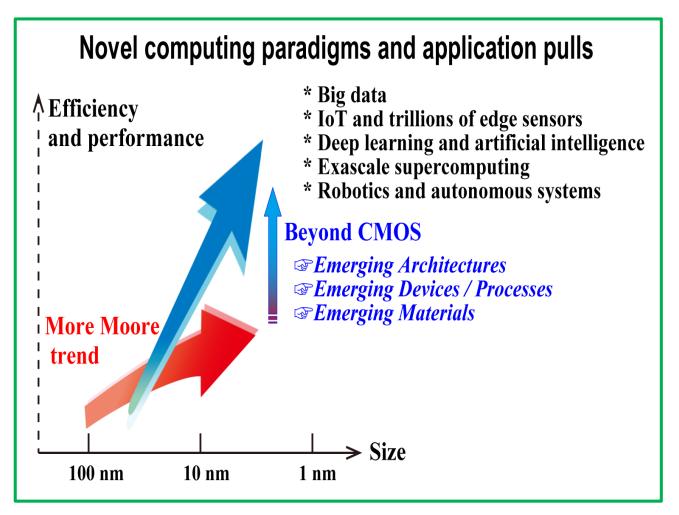

### **Change of paradigm for many applications**

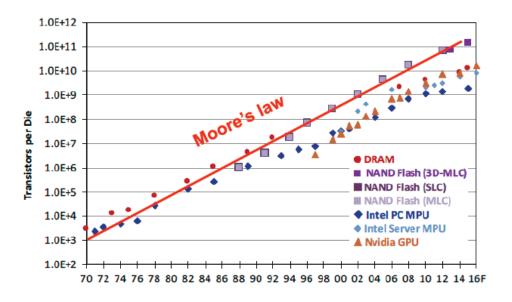

From More Moore ...

... to ...

More than Moore and heterogeneous integration

- From device density ...

- From device cost driven ...

- From single figure of merit ...

- From Technology push ...

- ... functionality increase

- ... system cost driven

- ... multiple parameters

- ... Application pull

- ... full supply chain

- ... sustainability

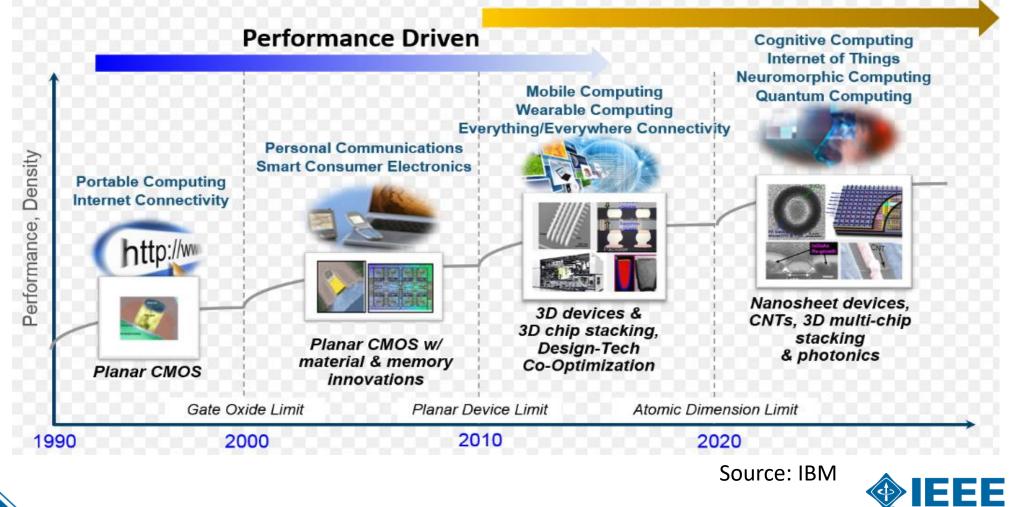

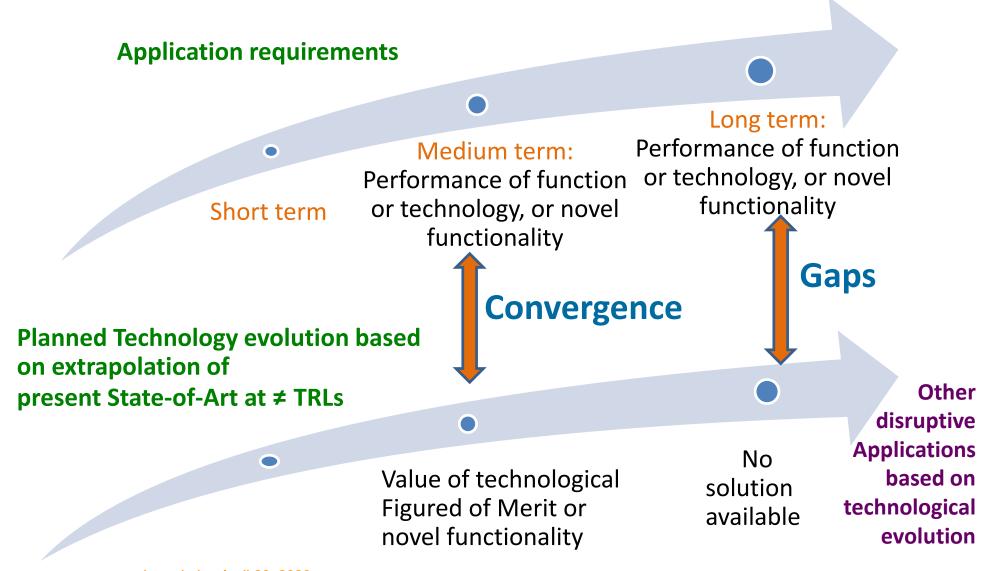

# At the same time: From performance-driven to application-driven device design

#### **Application Driven**

Page 3

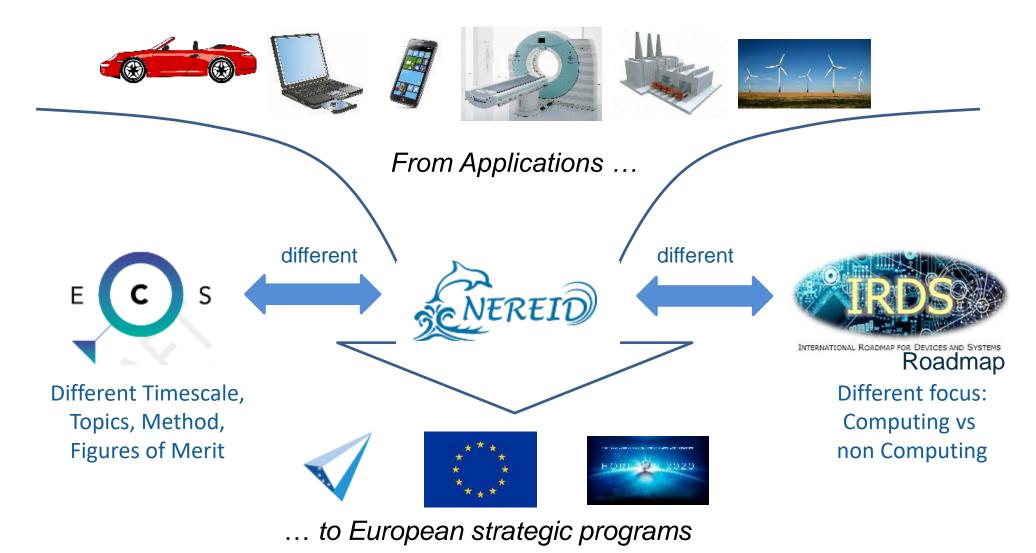

### **Complementarities: NEREID – ECS SRA - IRDS**

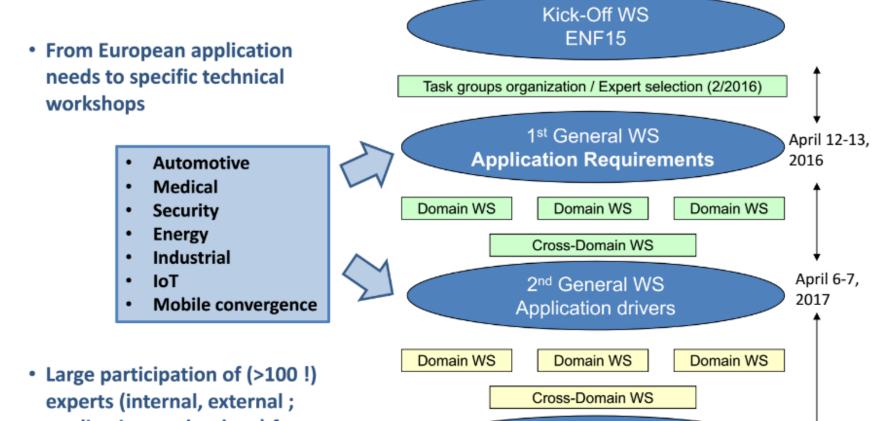

### **NEREID Roadmap Process**

Conclusive WS

Roadmap finalization

experts (internal, external; application, technology) from leading European academic and industrial institutions in Workshops

2018

### **NEREID Structure & coordination with other regions**

Management

Dissemination

Ø

Communication

Beyond CMOS

Advanced Logic and Connectivity

**Functional diversification**

System Design & Heterogeneous Integration

Equipment & Manufacturing Science **Coordination with roadmap initiatives**

#### **Advisory Committee**

10-15 high level members: Europe, USA, Asia

### **The NEREID Approach**

### **IRDS Chapters**

- Application Benchmarking

- System and Architecture

- More Moore

- Beyond CMOS and Emerging Research Materials

- Cryogenic Electronics & Quantum Information Processing

- Outside System Connectivity

- Yield Enhancement

- Factory Integration

- Lithography

- Environment, Health, Safety and Sustainability

- Metrology

- Packaging Integration

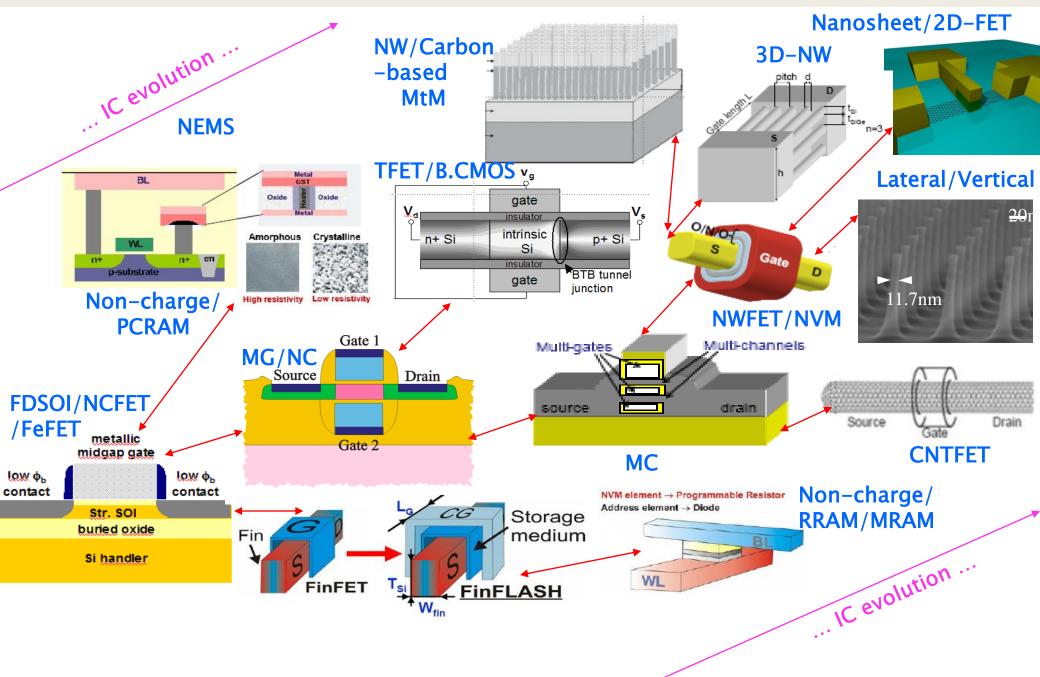

# Advanced Logic / Nanoscale FETs (NEREID & IRDS)

#### Nanoscale device roadmap for low energy, scaling, high perf., new functionalities

# **Challenges for future Nanoscale devices**

- -High performance

- -Low/very low static and dynamic power consumption

- -Scaling

- -Low variability

- -Good reliability

- -Affordable cost

### Sub. Swing vs Year / Lg (mV/dec)(Sim.)

----- InAs TFET

-Bulk Si

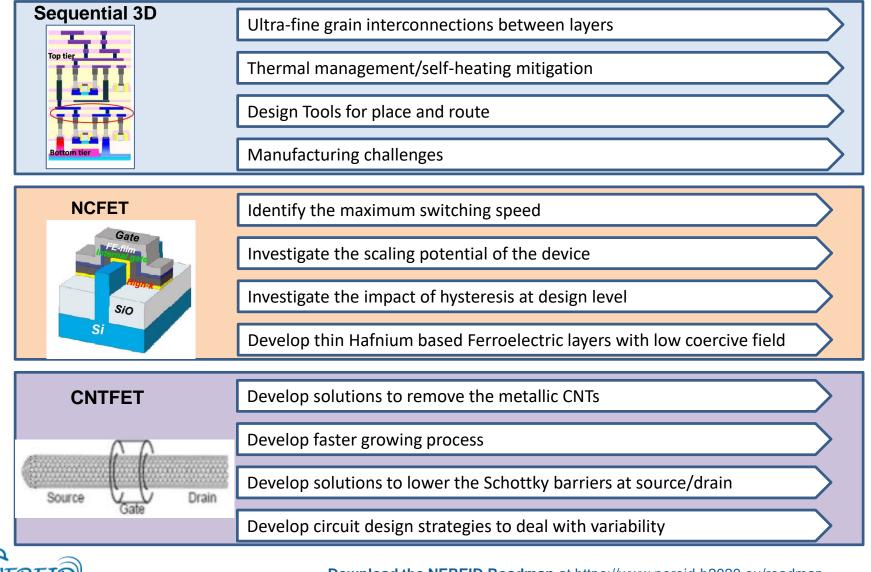

## **Research Priorities**

#### Advanced Logic and Memories (NEREID TASK 3.1)

- Nanowires

- FinFET

- FD-SOI

- Negative Capacitance FET (NCFET)

- Carbon Nanotubes (CNTFET)

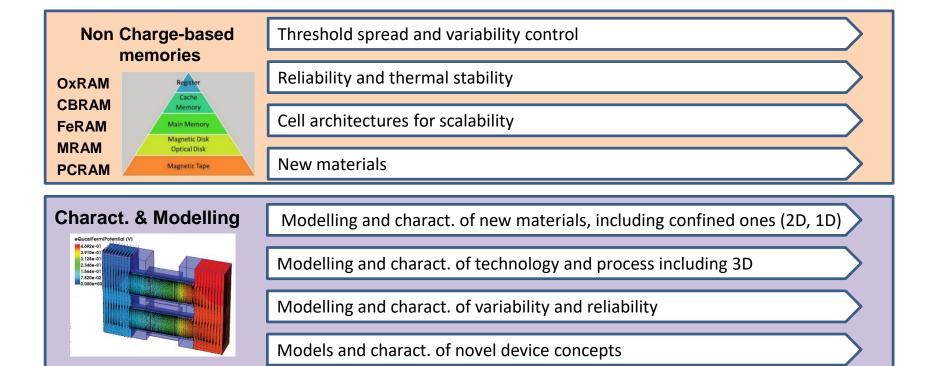

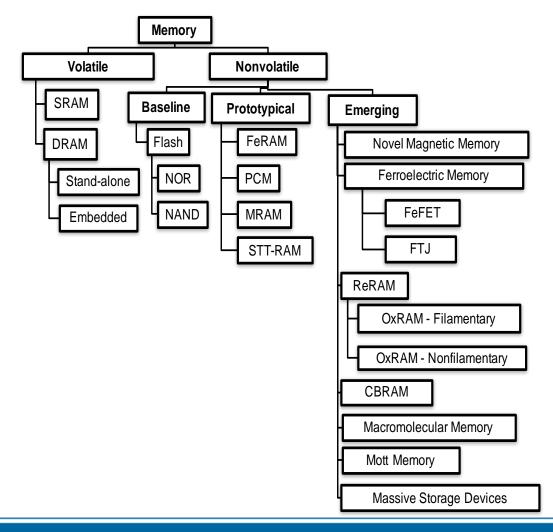

- Memories, Concept 1 OxRAM:

- Memories, Concept 2 CBRAM

- Memories, Concept 3 PCM

- Memories, Concept 4 MRAM

- 3D sequential integration

- Reliability, Characterization, Modelling

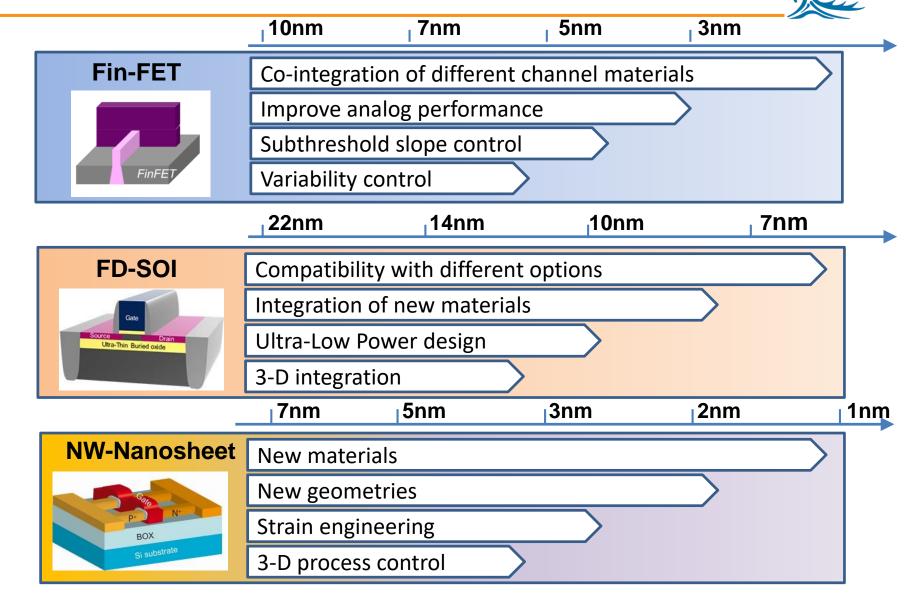

### Nanoscale FETs: Research highways

### Nanoscale FETs: Research highways

### Nanoscale FETs: Research highways

### **IRDS Roadmap 2018**

INTERNATIONAL ROADMAP FOR DEVICES AND SYSTEMS

| YEAR OF PRODUCTION                              | 2018   | 2020    | 2022           | 2025       | 2028         | 2031            | 2034            |

|-------------------------------------------------|--------|---------|----------------|------------|--------------|-----------------|-----------------|

|                                                 | G54M36 | G48M30  | G45M24         | G42M21     | G40M16       | G40M16T2        | G40M16T4        |

| Logic industry "Node Range" Labeling (nm)       | "7"    | "5"     | "3"            | "2.1"      | "1.5"        | "1.0 eq"        | "0.7 eq"        |

| IDM-Foundry node labeling                       | i10-f7 | i7-f5   | i5-f3          | i3-f2.1    | i2.1-f1.5    | i1.5e-f1.0e     | i1.0e-f0.7e     |

| Logic device structure options                  | FinFET | finFET  | finFET<br>LGAA | LGAA       | LGAA<br>VGAA | LGAA-3D<br>VGAA | LGAA-3D<br>VGAA |

| Mainstream device for logic                     | finFET | finFET  | finFET         | LGAA       | LGAA         | LGAA-3D         | LGAA-3D         |

|                                                 | Oxide  | S Cosde | Oxide          | Oxide      | Oxide        | Oxide           | Oxide<br>Oxide  |

| LOGIC DEVICE GROUND RULES                       |        |         |                |            |              |                 |                 |

| Mx pitch (nm)                                   | 40     | 36      | 32             | 24         | 20           | 16              | 16              |

| M1 pitch (nm)                                   | 36     | 32      | 30             | 21         | 20           | 20              | 20              |

| M0 pitch (nm)                                   | 36     | 30      | 24             | 21         | 16           | 16              | 16              |

| Gate pitch (nm)                                 | 54     | 48      | 45             | 42         | 40           | 40              | 40              |

| L <sub>a</sub> : Gate Length - HP (nm)          | 20     | 18      | 16             | 14         | 12           | 12              | 12              |

| Beyond-CMOS as complimentary to mainstream CMOS |        |         | -              | 2D Device, | 2D Device,   | 2D Device,      | 2D Device,      |

|                                                 | -      |         |                | FeFET      | FeFET        | FeFET           | FeFET           |

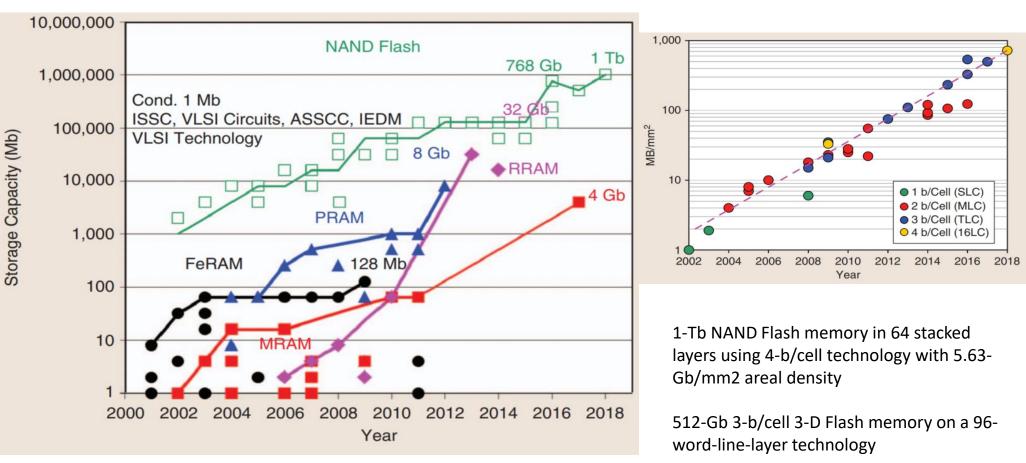

### **3D NAND – IRDS roadmap**

| -                                                          |          |          |          |          |           |             |             |

|------------------------------------------------------------|----------|----------|----------|----------|-----------|-------------|-------------|

| YEAR OF PRODUCTION                                         | 2018     | 2020     | 2022     | 2025     | 2028      | 2031        | 2034        |

|                                                            | G54M36   | G48M30   | G45M24   | G42M21   | G40M16    | G40M16T2    | G40M16T4    |

| Logic industry "Node Range" Labeling (nm)                  | "7"      | "5"      | "3"      | "2.1"    | "1.5"     | "1.0 eq"    | "0.7 eq"    |

| IDM-Foundry node labeling                                  | i10-f7   | i7-f5    | i5-f3    | i3-f2.1  | i2.1-f1.5 | i1.5e-f1.0e | i1.0e-f0.7e |

| Mainstream device for logic                                | finFET   | finFET   | finFET   | LGAA     | LGAA      | LGAA-3D     | LGAA-3D     |

| FLASH TECHNOLOGY                                           |          |          |          |          |           |             |             |

| 2D NAND Flash uncontacted poly 1/2 pitch – F (nm) [1][2]   | 15       | 15       | 15       | 15       | 15        | 15          | 15          |

| 3D NAND minimum array 1/2 pitch - F(nm) [3]                | 80       | 80       | 80       | <80      | <80       | <80         | <80         |

| Number of word lines in one 3D NAND string [4]             | 48-64    | 64-96    | 96-128   | 128-192  | 256-384?  | 384-512?    | 512+?       |

| Dominant Cell type (FG, CT, 3D, etc.) [5]                  | FG/CT/3D | FG/CT/3D | FG/CT/3D | FG/CT/3D | FG/CT/3D  | FG/CT/3D    | FG/CT/3D    |

| Product highest density (2D or 3D)                         | 512G     | 1T       | 1T       | 1.5T     | 3T        | 4T          | 4T+         |

| 3D NAND number of memory layers [6]                        | 48-64    | 64-96    | 96-128   | 128-192  | 256-384?  | 384-512?    | 512+?       |

| Maximum number of bits per cell for 2D NAND [7]            | 3        | 3        | 3        | 3        | 3         | 3           | 3           |

| Maximum number of bits per cell for 3D NAND [8]            | 3        | 4        | 4        | 4        | 4         | 4           | 4           |

| Chip area at maximum number of bits (mm <sup>2</sup> ) [9] | 140      | 140      | 140      | 140      | 140       | 140         | 140         |

| Bit density at maximum number of bits/cell (Bits/cm2) [10] | 3.66E+11 | 7.31E+11 | 9.75E+11 | 1.46E+12 | 2.93E+12  | 3.90E+12    | ?           |

|                                                            |          |          |          |          |           |             |             |

2018: 64-96 layers, 0.7-1 Tbits

2034: 512+ layers, >6 Tbits

### 1Tb (64 layers, 4b/cell) 3D-NAND

Source: ISSCC 2018

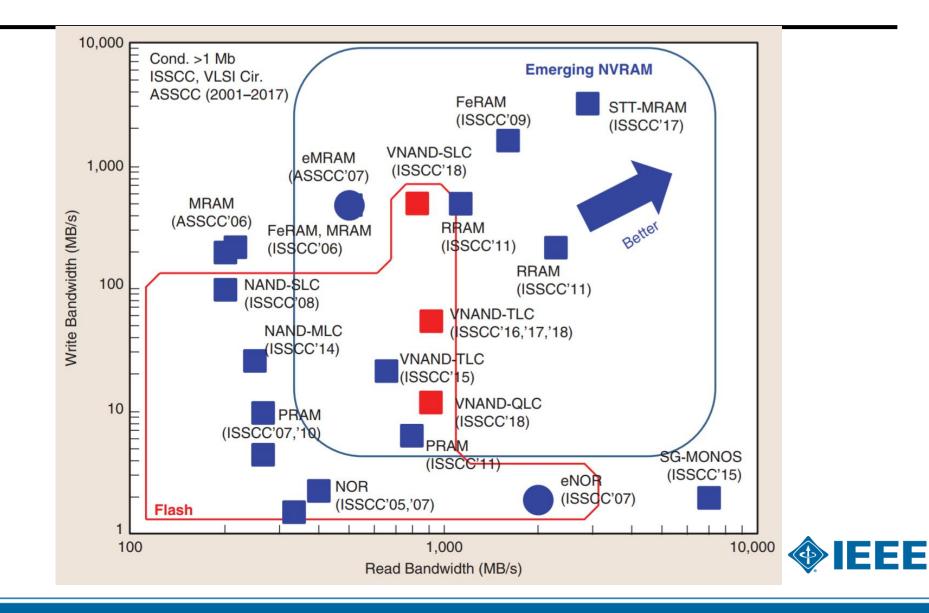

### Non-charge-based memories for embedded applic.

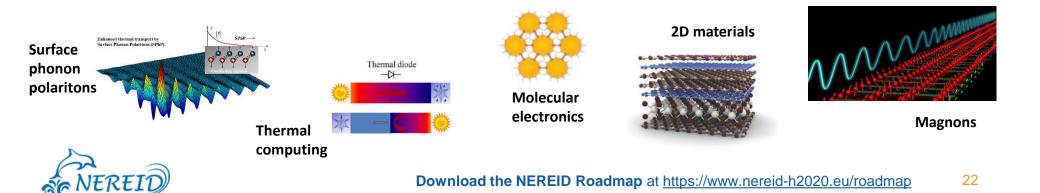

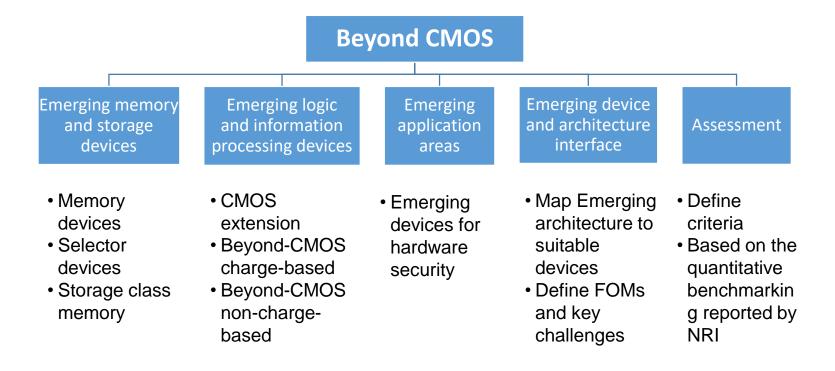

# Beyond-CMOS (NEREID & IRDS)

Imep-Lahc, April 29, 2020

#### **Opportunities in the Beyond CMOS field**

- New state/hybrid state variables: spin, magnon, phonon, photon, electronphonon, photon-superconducting qubit, photon-magnon, etc...

- States can be digital, multilevel, analog, entangled...

- Low power: Spintronics, magnons, even entropy-based computing

- High speed: 2D systems, valleytronics (~100 fs relaxation times)

- Applications in information processing: best suitable variables can be combined for efficient operation (e.g. optomechanics for light to mm-wave conversion, neuromorphics for various pattern recognition tasks)

### **Objective of Beyond CMOS Chapter**

#### **BC Chapter Organization**

"Emerging Research Materials" will be rolled into the Beyond-CMOS chapter

#### **Emerging Memory Devices**

### **Logic and Information Processing Devices**

#### State variable Transistor laser Non-charge Nanomagnetic logic Spin wave Excitonic SpinFET **CNT FET** NW FET Charge Neg-C<sub>g</sub> FET TFET p III-V n Ge Si FET 2D Channel FET Mott FET NEMS Conventional Novel Structure /materials

### **IRDS Emerging Research Materials for:**

- More Moore

- Logic (Structure (finFET, LGAA, VGAA), channel material (Si, SiGe, Ge, III-V), Doping, Contacts, Gate Stack)

- Memory (DRAM, NVM)

- Beyond CMOS

- Emerging logic and information processing (2D materials, CNTs, spin, Mott, negative capacitance, nanomagnetic, excitonic, photonic, NEMS)

- Emerging memory and select (ReRAM, magnetic, ferroelectric, Mott)

- Lithography and patterning

- Interconnect

- Packaging and heterogeneous integration

- Outside system connectivity

- Emerging and/or disruptive convergent technologies (Mobile, IoT, Sensors, Energy, Medical)

#### **Emerging Device-Architecture Interaction**

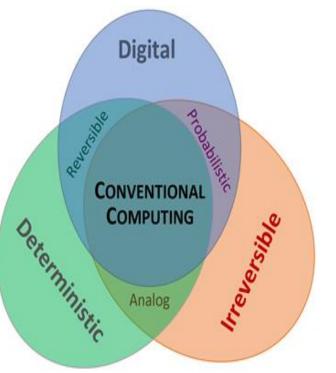

#### Analog computation

- Analog crossbar architectures

- Matrix vector multiplication (MVM) and vector matrix multiplication (VMM)

- Outer product update (OPU)

- Field programmable analog array (FPAA)

- Resistive memory crossbar solver

- Ternary content addressable memory

- Neural computing and crossbar architectures

- Analog neuron functional block (ANFB)

- Magnetic cellular neural network

- Computing with dynamical systems

- Computing with coupled oscillators

- Chaotic logic

- Analog architecture and energy minimization

- Probabilistic circuits

- Reversible computing

Categorization of conventional vs. alternative computing paradigms

### **Research Priorities**

### **Criteria:**

- Potential for data processing

- Time scale ~10-15 years

Beyond-CMOS – Emerging devices and Computing Paradigms (NEREID Workpackage 2, WP2)

- Steep slope switches: Tunnel FETs

- Neuromorphic circuits and computing

- Spintronics

- Quantum Photonics

- Phonon, Brownian and nano-opto-mechanical computing

### **Tunnel FETs**

### **Opportunities**

- Operation based on band-to-band tunneling

- Sub-thermionic subthreshold slope, S<60 mV/dec at RT</li>

- Supply voltage scaling -> 0.2-0.3 V

- Low power consumption

- c at RT

- Von Neumann architecture applies -> compatible with current circuit designs

- 2D/2D TFET architecture

- Analog gain at low I/V

### Challenges

•Low I<sub>ON</sub> -> Low operation speed

•Materials and interfaces (traps degrade the operation)

Scaling may be an issue

Design tools for TFET circuitry are missing

### **Neuromorphic Computing**

### **Opportunities**

- Two approaches:

- HPC + algorithms, pattern recognition, data mining

- Specific hardware (digital, analog, mixed) with memory nodes

- Integration with CMOS platform

- Low power, high efficiency (sub-fJ energy per bit possible)

- Supervised/unsupervised learning

- Fast pattern recognition (images, text, medical etc.)

- Photonic synapses (optical fibres + PCM synapses)

- Degrees of freedom: Weighting of input can be multilevel, parallel or serial Challenges

- -Hardware development (CMOS neurons and PCM synapses, ...)

-Material issues, CMOS compatibility

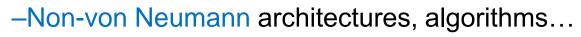

### **Spintronics**

### **Opportunities**

- Established technology for memories, STT-MRAM market growing

- Spins can be extra degrees of freedom in information processing

- Spin waves/magnons: No Joule heating, potential for THz operation

- Logic circuits have been demonstrated (switches, XNOR, majority gates)

- Fewer components, smaller footprint, low power consumption

- Neural networks have been demonstrated

- Tens of GHz microwave oscillators based on spin torque and spin Hall effect

- Topological insulators have potential for robust interconnects

Challenges

SEM image of a spin-valve device in which the charge and spin currents are separated

•Materials, interface and processing issues challenging

•Spin injection and read-out in spin FETs

•Magnetic field required in some cases

### **Beyond-CMOS:** Research Highways

- Nanofabrication affects most of the emerging technologies impacting variability of critical dimensions and processing defects. Novel approaches are required for *dimensional and compositional nanometrology*, accompanied by a traceable measurement protocol and to-be-developed instrumentation

- Manufacturability (non-standard processes, bottom-up approach in many cases, tolerances, lab-scale)

- Operation conditions (temperature, magnetic field...)

- Architectures (interconnects, variability, amplification, various functions for logic operations, memory, programming)

- Figure of Merits difficult to define before standardization (different operation principles for each area/technology)

- Identify common technological and design challenges to most emerging Beyond CMOS approaches as first step to overcome them and advance to higher TRLs.

- Foster collaborative projects between Academia and Industry on long term topics

#### Cryogenic Electronics and Quantum Information Processing (IRDS)

### -Superconductor Electronics

-Cryogenic Semiconductor Electronics

-Quantum Information Processing

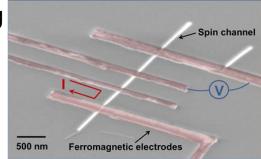

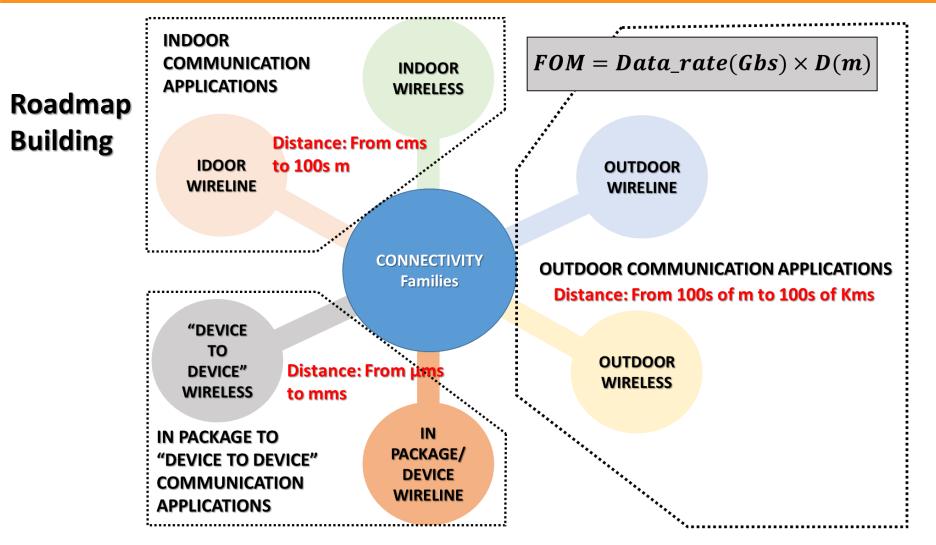

# Connectivity (NEREID & IRDS)

# **Research Priorities**

### Connectivity (Wireline and Wireless) (NEREID TASK 3.2)

- The Outdoor Wireless Applications

- The Outdoor Wireline Applications

- The Indoor Wireless Applications

- The Indoor Wireline Applications

- The Device to Device Wireless Applications

- The In Package/Device Photonics Wireline Applications

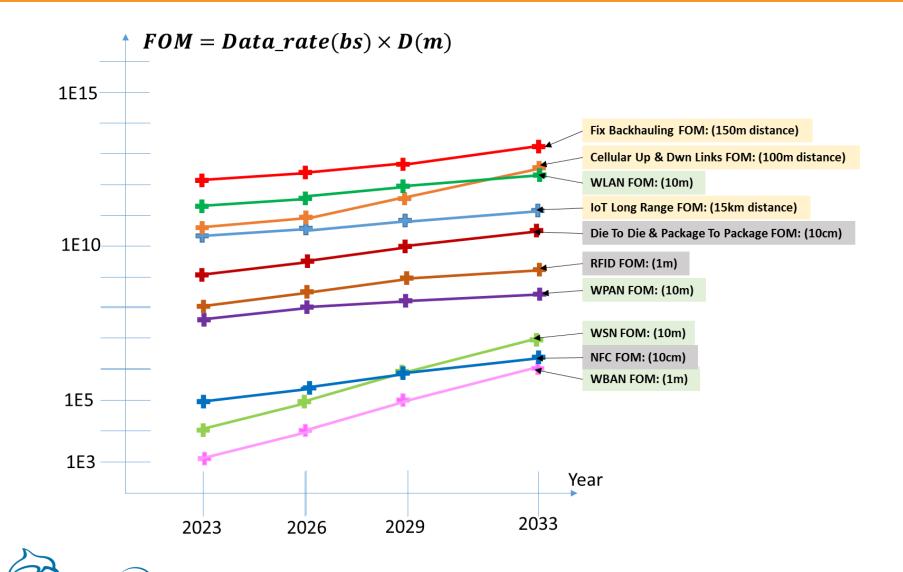

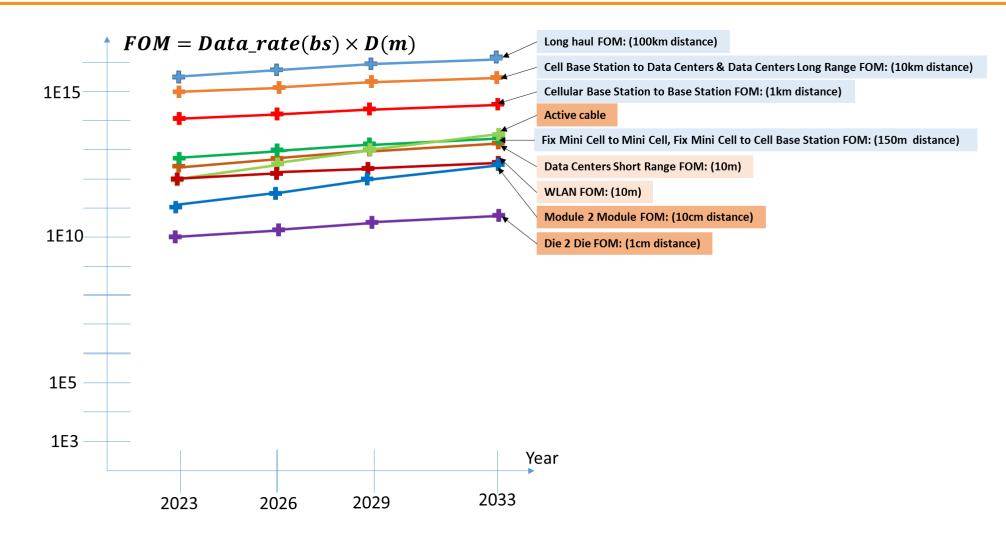

## **Connectivity Roadmap**

Imep-Lahc, April 29, 2020

# **3. Roadmap Building**

#### **3.31 Wireless Connectivity-FOM**

#### **3.32 Wireline Connectivity-FOM**

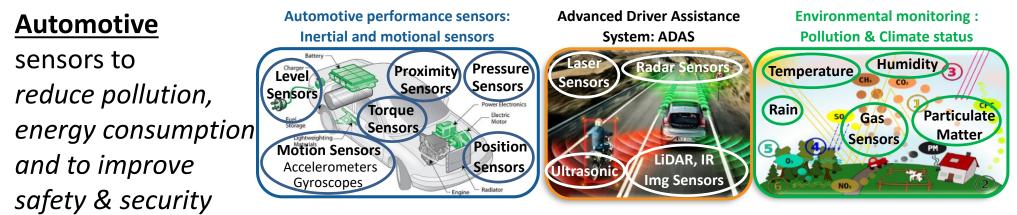

# Functional Diversification Smart Sensors

### Smart Sensors (NEREID TASK 4.1)

#### Sensors for Automotive applications:

-Sensors for navigation and car's basic system performance \*Motion Sensors \*Pressure Sensors -Advanced drive assistance systems (ADAS) for autonomous cars \*Images Devices \*Radar Sensor -Pollution/Air quality monitoring based on gas sensors Sensors for medical and healthcare applications: -Physiological Signal Monitoring -Implantable sensors: Bionics -Molecular Diagnostics

## **Smart Sensors - Roadmap**

- Improve accuracy

- Share manufacture infrastructure costs with other applications

#### Medical and healthcare

sensors are developing very fast.

#### Applications

- Drug Development

- Patient Monitoring

- Clinical Operation

- Clinical Imaging

- Fitness & Wellness

#### Devices

#### **End Users**

- Patients

- Biotech companies

- Research labs

- of pharma Healthcare providers

- & players

- Government authority

- Cost and convenience (for the patient, the hospital, etc.)

- Long and tedious development stage

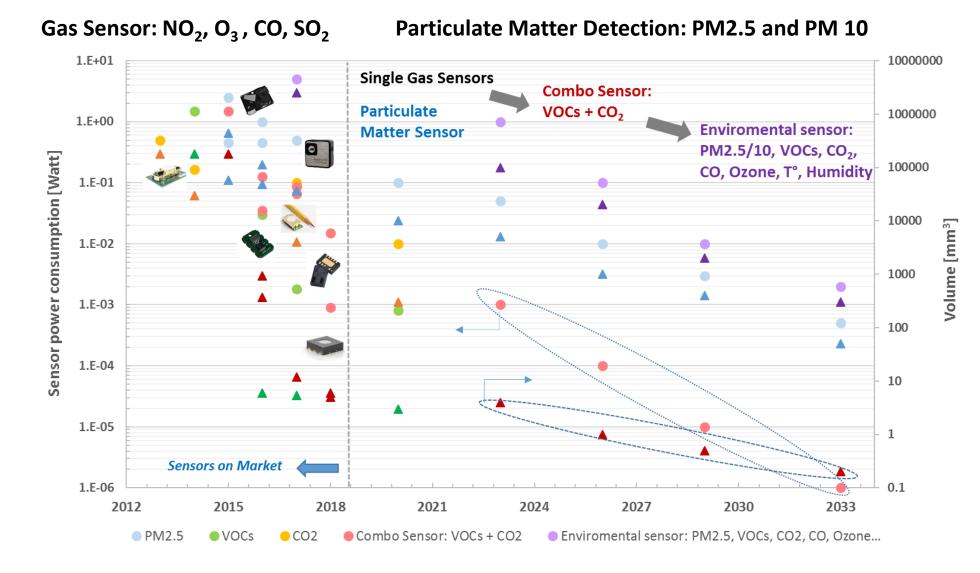

### Pollution/Air quality monitoring with gas sensors

## **Highlights of Smart Sensors**

Healthcare and automotive are of high relevance for European industry and research. In this sectors quality is even more important than the price.

- Well-penetrated healthcare systems

- Dominates the **autonomous vehicle market** with major technology manufactures and early commercialization of **ADAS systems**.

Some of the smart sensor identified gaps by 2030 concern: manufacturability and cost (hybrid integration), low power consumption (energy efficiency, zero-power or self-powered sensors), robustness (stability) of design and in production reliability.

Lack of metrology & standards: clinical validation, FDA approvals...

- Lack of regulations: reduce emissions, dependence in oil...

- Auto-calibration or self-calibrated sensors

- Sensor packaging, compatibility and CMOS integration

- Connected objects and Internet of things (IoT)

- Sensor Fusion/ Wireless Sensor Network (WSN)

Sensors relevant in other segments:

- consumer electronics: motion MEMS

- industrial: image sensors

- infrastructure: air quality sensors

- defense: LiDAR

- etc.

# Functional Diversification Smart Energy

Imep-Lahc, April 29, 2020

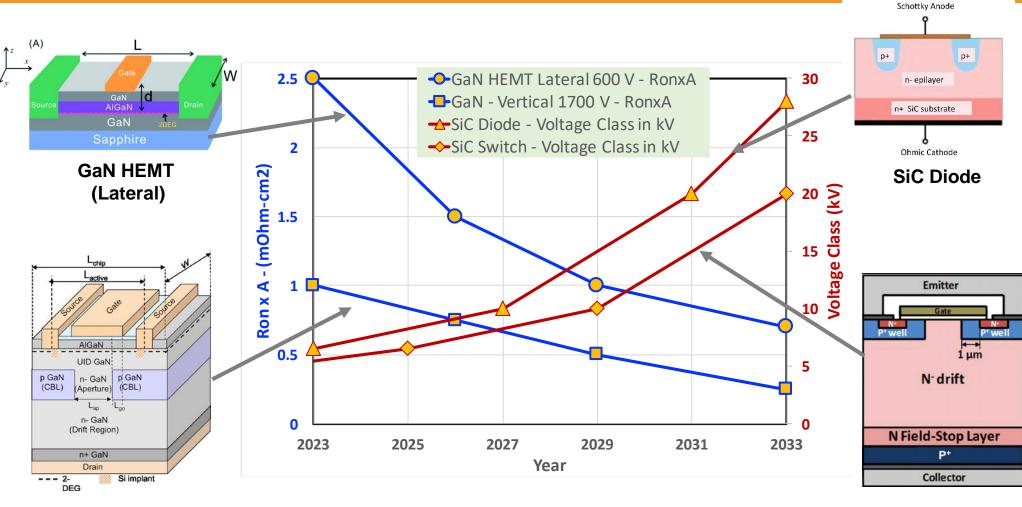

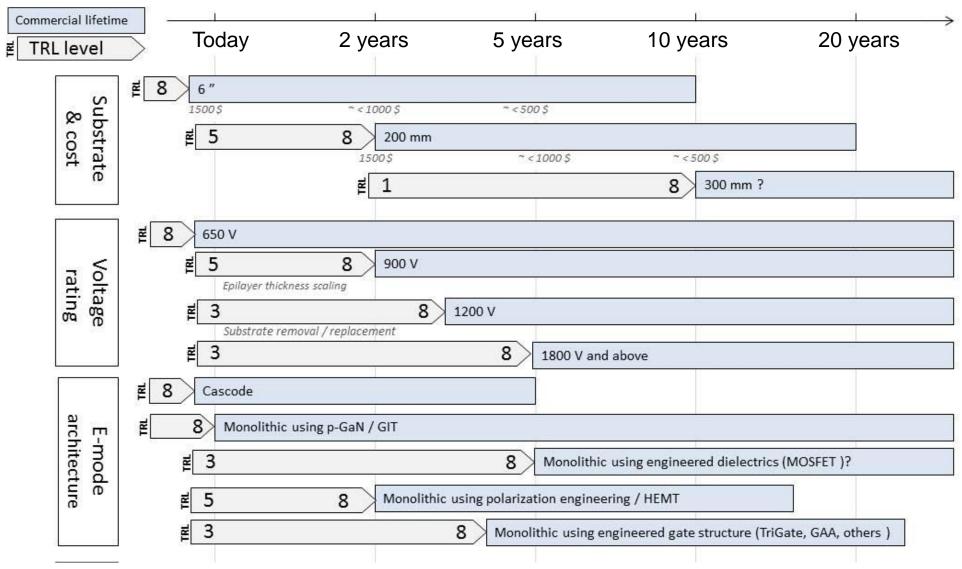

#### Smart Energy (NEREID TASK 4.2)

- Si based power devices

- GaN-devices and substrates

- SiC-based substrates

- Alternative Wide Bandgap Semiconductors: AIN, Ga2O3, Diamond

## **Smart Energy - Roadmap**

GaN Vertical

GaN/SiC Roadmap

SiC Switch

## **Smart Energy - Roadmap**

#### ➤GaN-on-Si Roadmap

## **Smart Energy devices open issues**

- Fast switching is the key for size and weight reduction with WBG power semiconductors leading to several issues: EMC, low parasitic inductances of the packaging and interconnection technologies, power losses related to passive components, need for system integration solutions, optimized switching cell, integrated drivers, ...

- As a consequence, the extreme miniaturization of power electronic systems leads to higher power density which requires new improved cooling techniques, but also leads to higher operation (and junction) temperature.

- ✤ Issues related to high temperature power electronics:

advanced materials and processes for **packaging** and interconnection (chip level and system level), polymer moulding & encapsulation, substrates, temperature range for passive components, **robustness** and reliability.

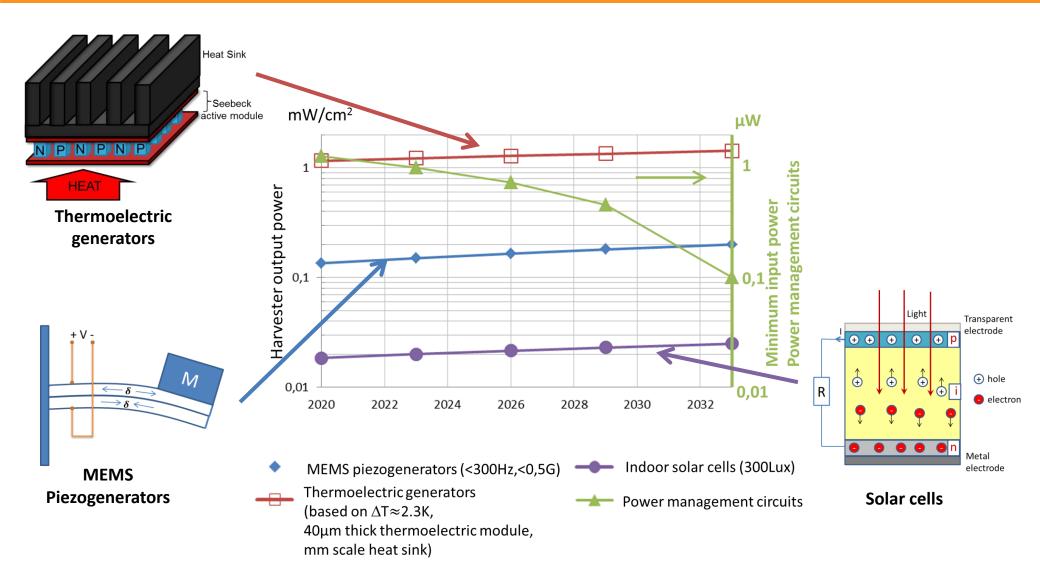

# Functional Diversification Energy for autonomous systems

#### Energy for Autonomous Systems (NEREID SubTASK 4.2.1)

- Mechanical EH: Electrostatic transduction

- Mechanical EH: Piezoelectric transduction

- Mechanical EH: Electromagnetic transduction

- Thermal energy harvesting

- Photovoltaic Energy Harvesting

- RF energy harvesting/wireless power transfer

- Energy storage Microbatteries

- Energy storage Microcapacitors

- Micro-Power Management

## **Energy for autonomous systems - Roadmap**

# **Highlights of Energy for autonomous systems**

- IoT and energy harvesting are application-driven today, so projects should mainly focus on the development of a complete application (from harvesting to the use case)

- The improvement of energy harvesters performance and efficiency is as important as the development of "green" materials.

- The use of nanotechnologies is foreseen to increase the performance of all the concepts in general.

- Increasing the bandwidth at a low frequency target (below 100Hz) will help to fit applications for vibration based mechanical energy harvesters.

- Power management circuits key issues: inductors size reduction, develop planar alternatives to inductors, reduce leakages.

# System Design and Heterogeneous Integration

### System Design and Heterogeneous Integration (NEREID Workpackage 5, WP5)

In this chapter, the main concepts are classified by connecting the three applications

- Automated Driving;

- Implantable Devices;

- Environmental Monitoring and Wearable Systems, with different elements of Application-Aware Hardware-Software-Co-Design. These Elements comprise Functionalities, Implementation Qualities and Criticalities and Needs.

# Equipment, Materials and Manufacturing Science

### Equipment and Manufacturing Science (NEREID Workpackage 6, WP6)

- More Moore

- More-than-Moore

- Manufacturing Science

# Thank you !

Download the NEREID Roadmap at <a href="https://www.nereid-h2020.eu/roadmap">https://www.nereid-h2020.eu/roadmap</a> Download the IRDS Roadmap at <a href="https://irds.ieee.org/">https://irds.ieee.org/</a>

**Contact :** <u>francis.balestra@grenoble-inp.fr</u>

Imep-Lahc, April 29, 2020